L2 or main memory), then it would be loaded into the new core. Once the data is available at a shared level of the memory architecture (e.g. First the original core will need to invalidate and clean the relevant cache lines out to the next level of the memory architecture. In a literal implementation of the MESI cache coherence protocol, it is quite inefficient for a migrated task to access memory locations that are stored in the L1 (write-back) cache of another core. In reality, unless explicit system calls bound a task to a specific core (this is known as _CPU affinity_), the likelihood is that that task will at some point migrate to a different core, along with its data as it is used. At boot time, each core can select to partake in the _coherency domain_, in which case the SCU will maintain coherency between them.Īn important fact about symmetric multi-core processors is that the detail of which process runs on which core is controlled by the Operating System. The SCU effectively monitors the traffic between local L1 data caches and the next level of the memory hierarchy. In an ARM MPCore processor, the coherency protocol is implemented and managed by the Snoop Control Unit (SCU). Indicates that the subject cache, other than being up to date with the next level of memory hierarchy, is also stored (duplicated) in one or more other core’s caches. The subject cache line is present only in the current cache, and it is clean (it is up to date with the next level of the memory hierarchy, L2 cache or main memory). The subject cache line is present only in the current cache and it is dirty (not up to date with the next level of the memory hierarchy, L2 cache or main memory). In a correctly configured system, every cache line is dynamically marked with one of the following states:

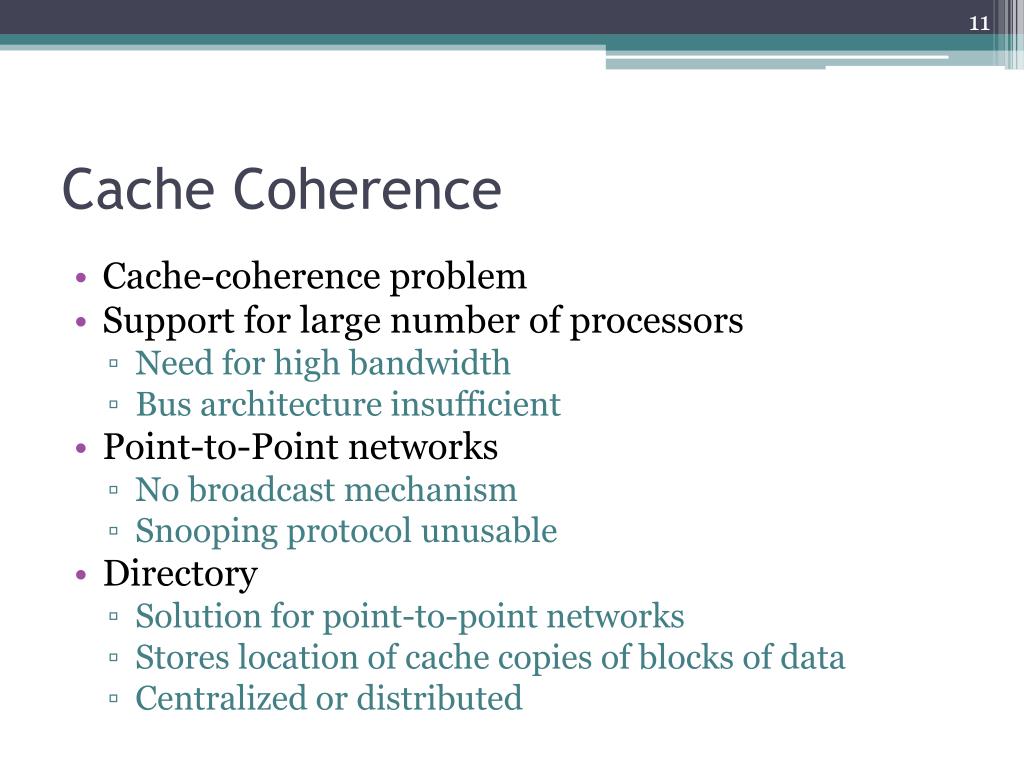

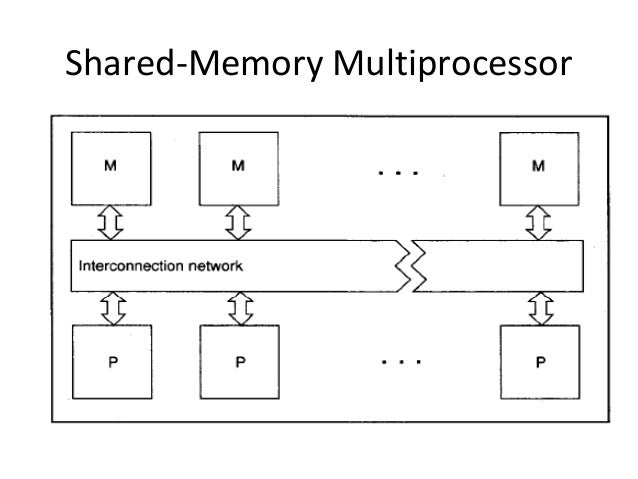

The ARM11 MPCore and Cortex-A9 MPCore processors support the MESI cache coherency protocol. A hardware control unit automatically manages the states. This is implemented by tagging all cache line with an identifier of their state in respect to overall system coherency and cache lines in other cores. The cache coherency protocol is a state machine that governs the condition of each cache line in each core’s cache at a given time. In a cached, shared memory, multi-core system, the mechanism implemented to maintain coherency between all CPUs’ local caches is called the cache coherency protocol. When enabled, the SCU automatically maintains coherency between the data caches local to each CPU.Ĭoherency Protocols in ARM MPCore Processors Processors such as the ARM11 MPCore and the Cortex-A9 MPCore feature a hardware block known as the Snoop Control Unit (SCU). When these cores feature local caches, a mechanism must be used to keep them coherent. Generally an Operating System would be running across all cores, transparently distributing tasks. The concept of Symmetric Multi-Processing (SMP) refers to a processor composed by two or more equivalent cores sharing main memory with equal access rights to it. This document highlights features and behaviors of the underlying hardware and provides guideline recommendations for developers so developers can use and program the DMA engine efficiently.Ĭache Coherency in Multi-Core Processing Systems

#Cache coherence cortex a9 driver

The target audience for this document is kernel level programmers, device driver developers and firmware designers that need to program at a low level on a coherent shared memory ARM system. This Application Note explores the implications associated with performing Direct Memory Access (DMA) operations on an ARM multi-core system such as the ARM11 MPCore and Cortex-A9 MPCore.

0 kommentar(er)

0 kommentar(er)